Frequently asked questions:

What's different between using the new 1149.1-2013

and 1687-2014?

The approaches are philosophically different. 1149.1-2013 requires IP or "instruments" to have a Test Data Register interface provided by the instrument provider. The silicon instruments must operate via only the TAP pins, System clocks, power and system reset. All instruments must be re-useable at board and system level in order to get correlation with ATE based tests and rapidly improve yield learning. With both IEEE 1500 and IEEE 1149.1-2013 the scope of IC and board test is completely covered for the most complex instruments. 1687 introduces a new insertion langauge called ICL. The verilog-like langauge requires more specific connections of wires, gates, muxes where 1149.1-2013 takes a more abstract approach to describing IEEE 1500 wrappers and instruments. 1687-2014 has a focus on legacy IP which does not have a TDR, manufacturing scan chains and using IC pins to access instruments. This affects the abilty to re-run tests in the system due to the pin demands, lack of structured IC resets, complexity and need for manual PDL 'fix-up' for un-wrapped legacy instruemnts.

What's included in the free

download?

Windows NEBULA TCP/IP Client software with

base features of:

- BSDL library for common devices

- IEEE 1149.1-2013 BSDL database compiler with extensions for internal Test

Data Registers

- IEEE 1149.1-2013 PDL scripting language

- TCL interpreter with extensions for 1149.1-2013

- TK GUI developer with concurrent multi-instrument operation

- Single Step Debugger for PDL/TCL with breakpoints

- Register/Mnemonic Spreadsheet interactive viewer & control

- Pin toggler - Put devices in EXTEST and toggle outputs and observe inputs

- Program FPGAs and CPLDs via SVF

- SVF support - Record and Apply SVF

- SVF Single Step with stop-on-fail

- WGL Support - Record WGL patterns and Apply WGL patterns

from Synopsys TetraMAX

- Web based updates

- Optional paid remote support

iJTAGServer Intellitech Simulation Interface

Server - for VCS on Redhat Linux 64 bit, Cadence Incisive or Mentor Questa (Linux or Windows 64-bit).

iCableServerX- Intellitech's Window's

based cable server for Xilinx's USB Cable II JTAG Controller.

iCableServerA- Intellitech's Window's

based cable server for the Intel/Altera USB JTAG Controller.

iCableServerD- Intellitech's Window's

based cable server for the Digilent USB JTAG HS2 Controller.

Alarm Clock example files - Source and synthesized Verilog

with Internal Scan inserted by TetraMAX, BSDL and BSDL

extensions, Mnemonic support, TCL/PDL example files, Makefiles

for use with VCS on Linux-64. Example Instrument support for

Altera and Xilinx FPGAs.

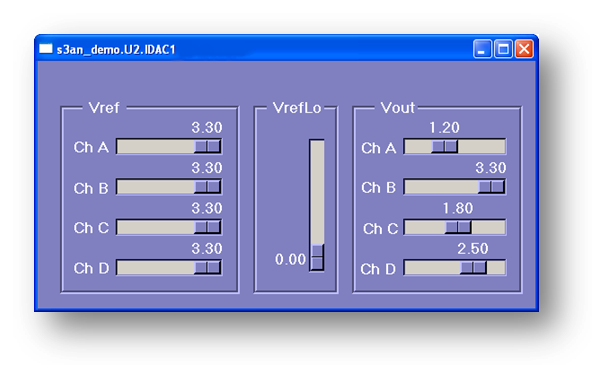

Xilinx Spartan 3AN Starter Kit - Training/Example files

The Xilinx Spartan 3AN Starter Kit is a popular low-cost PCB designed by Digilent with a Xilinx Spartan 3AN and DC/DC, DAC, ADC components from Linear Technologies. Spartan 3AN Starter Kit description. Verified Registered users can download the source files which include the Verilog for controlling the instruments, PDL and TCL and GUI TCL sources. The step-by-step demonstration with examples in PDL/TCL is here and can be viewed by verified registered users: Spartan3AN Starter Kit Demo

A simple example script in PDL, the new language of IEEE 1149.1 is as follows. This sets a voltage on the LTC2624 DAC available on the PCB.

iScope s3an_demo.U1.SPI_MUX # set the scope to SPI instrument

iWrite SELECT DAC1 # set the DAC to talk on the SPI bus

iApply # send the data over the cable

iScope s3an_demo.U1.DAC1 # DAC instrument

iWrite command WRINREG_UPD # set the write-update command for the DAC

iWrite ADDRESS DAC_A # set DAC_A (not DAC_B)

iWrite DATA V_2P06V # set the DAC output to 2.06V

iApply # send the data over the cable

Each # character is a comment. The iApply takes the data and sends it to the target.

What's Coming?

IEEE 1149.1-2013 BSDL suffices for 3D-SIC stacks and 2.5D ICs. Contact Intellitech for information supporting IC to HBM (High Band Width Memory) and Hyper-Memory Cube (HMC).

Future:

- iCableServerX for 64 bit Linux. This is a Linux version

of the Intellitech Cable Server for the Xilinx USB pod.

- 64 bit RedHat Linux based NEBULA Client

- STIL pattern recording support

- Additional Simulator support. (Are you using a simulator/verification engine other than the three we support?)

Why is this Free? Is there a catch?

There is no catch. Free tools will enable 1149.1-2013 to have wide-spread adoption. Free

versions of NEBULA will enable leading companies to do real

productive work with JTAG based access to on-chip scan-chains

and at the same time enable Universities and research

institutions to perform useful research in the area of on-chip

JTAG DFx and Instrument register access. Users will be able to

validate the instrument drivers written in PDL or TCL against

the simulation of the instrument and then against the actual

hardware. With free software the community will have a common

platform to validate instrument drivers and develop unique

instruments - that can be validated pre-silicon and used for

silicon bring-up.

Intellitech benefits as more ecosystem is developed to

increase fault coverage for embedded JTAG test. Intellitech has

educated the industry for over ten years on how to reduce

functional test development by embedding access to on-chip JTAG

test features with Intellitech's SystemBIST IC. JAF Test, JTAG

Assisted Functional Test, breaks the system functional test

challenge down into smaller manageable parts. Test development

can be done with just an understanding of the micro-parts, how

to execute a PRBS test over a serial link for example, without

the developer needing to know the entire mission mode

functionality of the system.

Intellitech may offer additional free opportunities or

charge token fees of US$100 to US$400 for additional

capabilities in the future. A very small fee for a tool in this

class. Each year Intellitech may ask you to re-validate your

email address.

Is "free" a sustainable business model?

Intellitech's primary revenue is not from this version of

NEBULA but from our components, IP, patents, methodologies and

high-end testers. There are many quality free software packages

today from FPGA vendors for instance. Many segments of the

industry are also using forms of free software. DimDim web

conferencing is a good example. As the use of the standard

matures and new capabilities emerge, there will possibly be

features of NEBULA that we reserve the right to charge for. You

may choose not to purchase those features. Support is not

included with the free software. Documentation on how to

install and operate the software is provided. If this is not

sufficient you will need to purchase a support package at $595

for a five (5) hour block of support time.

In order to download your free copy of the NEBULA client,

Xilinx USB CableServer, and ISIS, you must register on the

website here: Register.

What can I do with this now?

The software will allow you to describe internal test data

registers which are accessible via JTAG and import them into

BSDL using register_fields and register_mnemonics BSDL

extensions. It is possible to use NEBULA to create fully

compliant PDL scripts for register access. If changes in PDL

develop as the standards finalize updates will be provided to

support PDL. You can simulate your design in VCS and connect to

the JTAG ports of your design in simulation to validate TCL

scripts with JTAG register access. When the actual IC is

available, you can use a low cost Xilinx USB pod ($250 sold by

Xilinx) to access the on-chip JTAG accessible registers. If you

have TetraMAX you can generate ATPG patterns to apply via JTAG

and get diagnostics from TetraMAX. You can also write generic

TCL scripts which you can record as WGL ATE tester patterns.

Engineers can also toggle pins, program FPGAs or write TCL

scripts to toggle pins. Intellitech's full software packages

have built-in support for board level ATPG, memory interconnect

and flash programming. It would be possible to create your own

TCL/TK scripts if you desire to emulate some of the high-end

functions of Eclipse our board test product.

In order to download your free copy of the NEBULA client,

Xilinx USB Cableserver and simulation interfaces, you must register on the

website here: Register.

|