1149.1-2013 JTAG/IJTAG Overview

The new 1149.1-2013 standard includes new BSDL

support for what the standard calls "Clause 9" design specific

test data registers. Some engineers call these UDRs, or User Test Data Registers. Internal TDR registers, Internal JTAG, has

always been part of the standard however BSDL did not provide a

method to describe these registers until now. The new langauge

syntax in 1149.1-2013 BSDL, includes extensions that support

internal scan register field definitions and mnemonics (easy

to remember words associated with values in the register). This

data is compiled into a database where a GUI or scripting

langauge can access the on-chip internal registers. NEBULA

comes with ready support for these important features. |

attribute

REGISTER_FIELDS of Example :

entity is

"init_data (

"&

"((504 DOWNTO

500) IS Clock[5] IWRITE: Clockset(F100Mhz) ),"&

"((302 DOWNTO

300) IS Protocol[3] IWRITE: Protocol (off) ), "&

"((101 DOWNTO

100) IS Voltage[2] ), "&

"(( 19 DOWNTO

0) IS Reserved [20])"&

")" &

“intscan

( "&

"((163 DOWNTO

100) IS Address[64] ), "&

“((227

DOWNTO 164) IS Data[64] ), "&

“((228)

IS WE[1] ),

"&

);”

IEEE 1149.1-2013 Register Fields Attribute |

A new language for accessing the on-chip

registers called PDL, Procedure Definition Language enables IP

providers and IP integrators to create non-device specific

scripts for reading and writing to the registers. Future IEEE

P1687 also uses the PDL langauge but prefers to describe

registers and scan-chains through a new format called ICL -

Instrument Connectivity Language. ICL is closer to verilog in

its complexity but gives P1687 a few more features for

supporting legacy devices with unplanned DFT architectures. As ICL becomes more

solidified and customer need arises, this will be added to

NEBULA. For the time being the momentum is from customers is behind 1149.1-2013.

These capabilities, now standardized, were first introduced in 1997 by Intellitech and

became the basis for Intellitech's NEBULA Silicon Debugger (NEBULA

Silicon Debugger) and other products. TCL or Tool Command

language is an open source language see www.tcl.tk. Intellitech pioneered using TCL with extensions for JTAG commands and named registers and mnemonics for in-situ on-chip access. In the 1990s, board test engineers selected visual basic and proprietary ICT langauges for JTAG, however TCL/TK is

used throughout the EDA industry for script development and

automation. Hence we have always seen it as a natural fit to access of on-chip IP or "Instruments". NEBULA fully supports PDL, TCL and TK.

The PDL and TCL language with extensions

enables scripts to be written that enable write and reads to

internal JTAG Test Data Registers and on-chip DFx structures

via the JTAG TAP. The major advantage of the approach is that

the scripts are re-targetable - there is no scan-chain bit and

shift information present like WGL or STIL ATE vector

languages. Unlike using Verilog for test benches, PDL/TCL give

the ability to validate JTAG/iJTAG based IP in simulation then

take the same PDL or TCL and execute against a real device. |

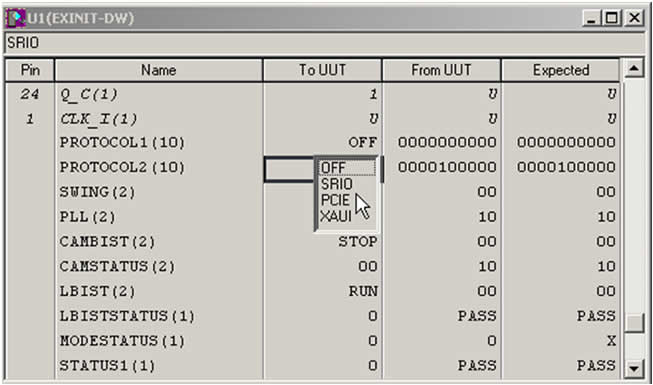

NEBULA GUI created from 1149.1-2013 BSDL

iProc myprocedure {

# PDL/TCL script

iScope U1

iWrite LBIST RUN # bit-position independent register

iApply

iRunLoop 300000

iRead LBISTSTATUS PASS # check that LBIST passed

iApply

# set differential Swing to 400mv

iWrite SWING S400MV

iWrite PROTOCOL1 SRIO # set protocol to SRIO

iApply

# execute CAM BIST

iWrite CAMBIST RUN

iApply

iRead CAMSTATUS DONE

iApply

}

PDL/TCL script to operate on registers.

Comments are preceeded by "#"

Free software

Click the link in the sidebar to the left to learn more about the capabilities of the free NEBULA software. In order to download your free copy of the NEBULA client,

Xilinx USB Cableserver and ISIS, you must register on the

website here: Register.

|