# Intellitech)(Intellitech)(Intellitech)(Intellitech

### itech)(Intellitech)(Intellitech)(Intellitech)(Inte

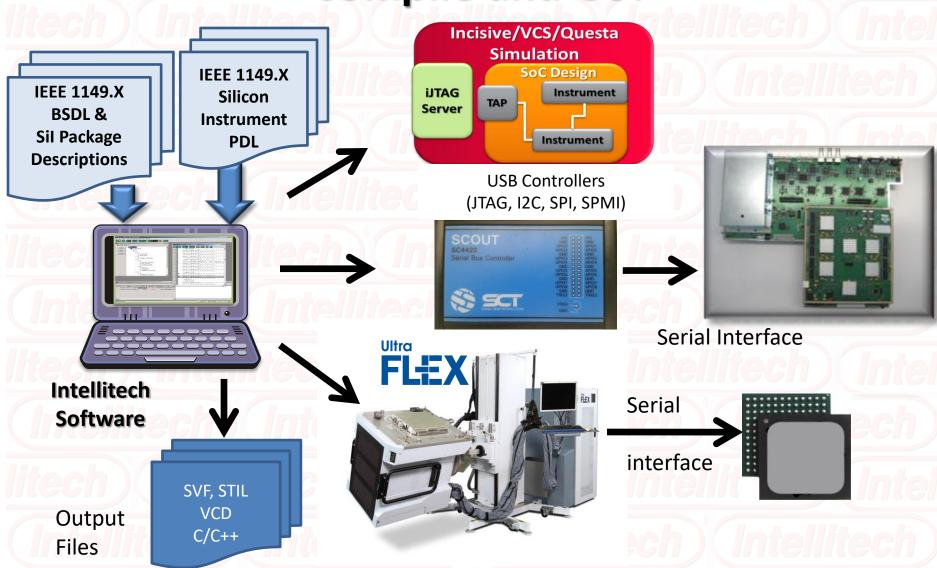

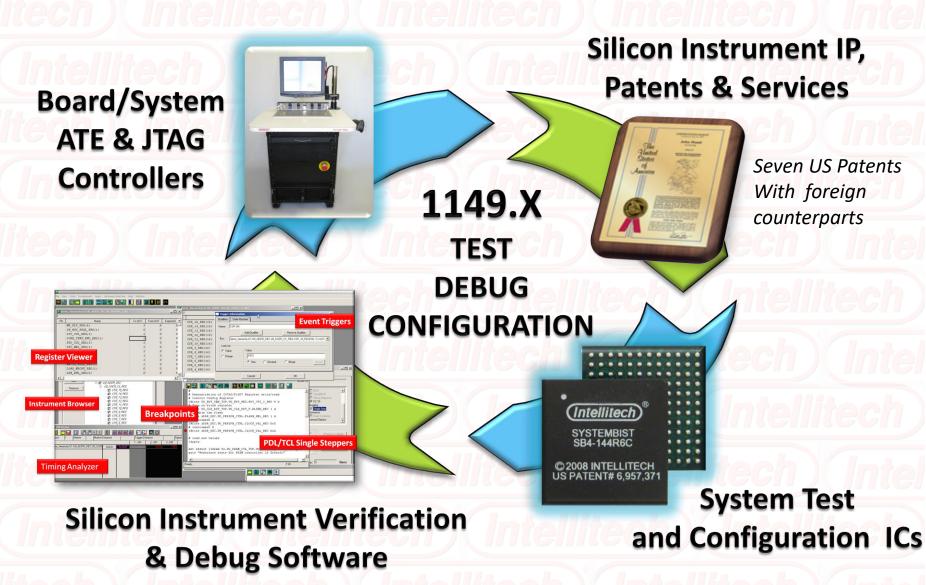

#### About Intellitech Corporation | IEEE 1149.x Solutions

Leading supplier of IEEE 1149.x based ATE & Software

**Headquarters in** Well **Privately Rochester, NH & Established Owned** Fujisawa, Japan 30+ Years **Stable long-term Proven 800+** investors Licensees Respected **Expertise Vision IEEE Standards Contributors**

### Intellitech)(Intellitech)(Intellitech)(Intellitech

## Intellitech - What we do

#### **Intellitech customer locations**

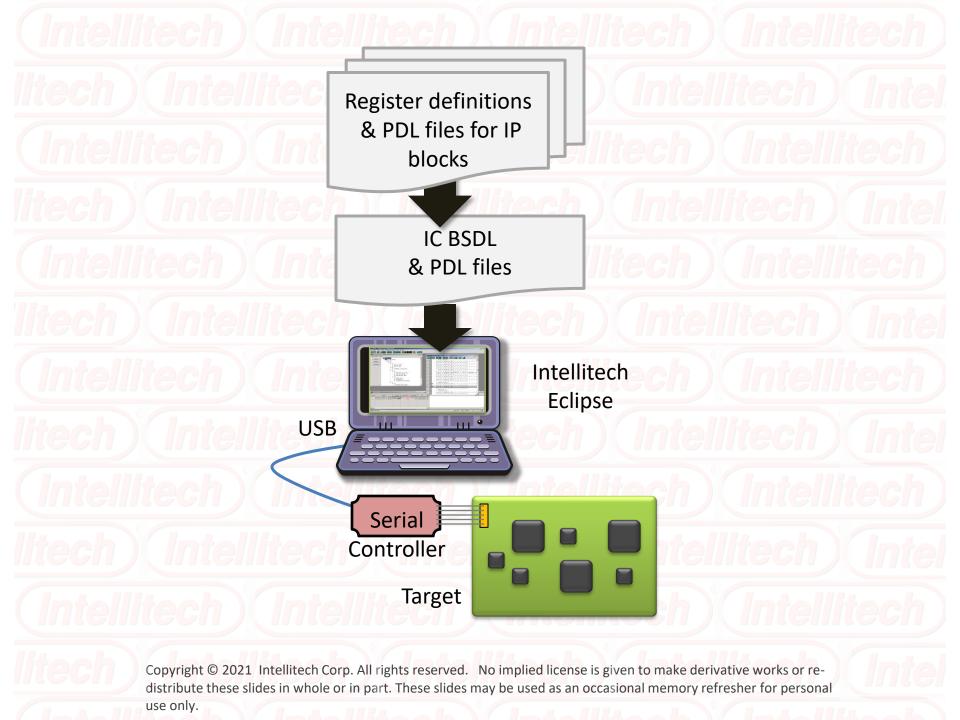

#### Intellitech's software is like a web browser for an IC, PCB or System

Google Chrome or Microsoft Edge Browser

use only.

WWW World Wide-Web

Serial Access

Intellitech

Eclipse

Copyright © 2021 Intellitech Corp. All rights reaches SNo implied license is give

Copyright © 2021 Intellitech Corp. All rights reaches SNo implied license is give

Copyright © 2021 Intellitech Corp. All rights reaches SNo implied license is give

Copyright © 2021 Intellitech Corp. All rights reaches SNo implied license is give

Copyright © 2021 Intellitech Corp. All rights reaches SNo implied license is give

Copyright © 2021 Intellitech Corp. All rights reaches SNo implied license is give

Copyright © 2021 Intellitech Corp. All rights reaches SNo implied license is give

Copyright © 2021 Intellitech Corp. All rights reaches SNo implied license is give

Copyright © 2021 Intellitech Corp. All rights reaches SNo implied license is give

Copyright © 2021 Intellitech Corp. All rights reaches SNo implied license is give

Copyright © 2021 Intellitech Corp. All rights reaches SNo implied license is give

Copyright © 2021 Intellitech Corp. All rights reaches SNo implied license is give

Copyright © 2021 Intellitech Corp. All rights reaches SNo implied license is give

Copyright © 2021 Intellitech Corp. All rights reaches SNo implied license is give

Copyright © 2021 Intellitech Corp. All rights reaches SNo implied license is give

Copyright © 2021 Intellitech Corp. All rights reaches SNO implied license is give

Copyright © 2021 Intellitech Corp. All rights reaches SNO implied license is give

Copyright © 2021 Intellitech Corp. All rights reaches SNO implied license is give

Copyright © 2021 Intellitech Corp. All rights reaches SNO implied license is give

Copyright © 2021 Intellitech Corp. All rights reaches SNO implied license is give

Copyright © 2021 Intellitech Corp. All rights reaches SNO implied license is give to the sound of the sou

distribute these slides in whole or in part. These slides may be used as an occasional memory refresher for personal

#### Do you specify Wifi for components and devices?

# Do you specify

IEEE 802.11g-2003

or

IEEE 802.11ax-2021

# Why give customers ICs that conform to IEEE 1149.1-2001 when what they need is IEEE 1149.1-2013?

# IEEE 1149.1-2013 (JTAG)

- Standardizes a plug-n-play test interface to IP blocks in an IC

- Standardizes a hierarchical structural language for the IP registers

- -Standardizes a procedural operation language (PDL) based on Tcl/TK

| Silicon Instru | Mission IP    |      |          |

|----------------|---------------|------|----------|

| Memory BISR    | Ext. DDR BIST | GPIO | Connecti |

SerDes BIST PLL Control

PVT monitors JTAG2AXI drivers

GPIO Connectivity

ADC Analog

DAC Etc.

Approved by over

120 industry experts 2021 Intellitech Corp. Fair is some sides may be used as an occasional memory refresher for personal use only.

7

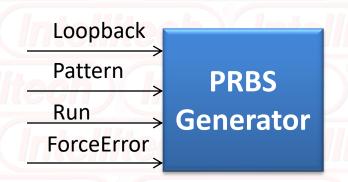

#### What does it look like?

- Describe Interface to IP w/o TAP

- Description is "packaged" in compliant

IEEE 1149.1-2013 package file

- Describe just interface + mnemonics

- Machine readable

```

Attribute REGISTER_MNEMONICS of SERPRBS : package is

"OnGroup (ON (1), OFF (0))," &

"PatGroup (PRBS31(1), PRBS23 (2), PRBS7(3))";

Attribute REGISTER_FIELDS of SERPRBS : package is

"PRBS [5] ( "&

"(Loopback [1] IS (4) DEFAULT(OnGroup(ON))), " &

"(Pattern [2] IS (3,2) DEFAULT(PatGroup(PRBS7))), " &

"(Run [1] IS (1) SAFE(OnGroup(OFF))), " &

"(ForceError [1] IS (0)) DEFAULT(OnGroup(OFF)))";

```

#### 1149.1-2013 Solution: Standardize the IP documentation

PDL = Procedural Description Language

- new vectorless re-targetable

language for describing IP operation

- Hierarchical (Self-contained for the IP)

| Set data       | iWrite        | Loopback | ON     | 'n |

|----------------|---------------|----------|--------|----|

|                | <b>iWrite</b> | Pattern  | PRBS23 |    |

|                | <b>iWrite</b> | Run      | ON     | 6  |

| Intellitech (  | iRead         | Result   | PASS   | n  |

| Shift data     | iApply        |          |        |    |

| raan II Inteli |               |          |        |    |

Format: <iWrite > <Register> <value or mnemonic>

#### Register documentation alone is not enough!

- Customer wants pre-engineered solution

- Instrument and software plug 'n play

- Need robust language (math operations, logical operations, etc) needed to make sense of data scanned out

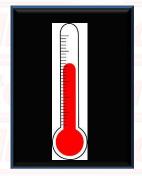

#### Temp Monitor

$$Voltage = 10 \times \frac{\kappa T}{q} \times \ln(10)$$

#### **IEEE 1149.1-2013 PDL required!**

iProc read {} {

set reg [iGet tempregister]

set temp = ([\$reg x 503.975] / 4096) - 273.15

return \$temp

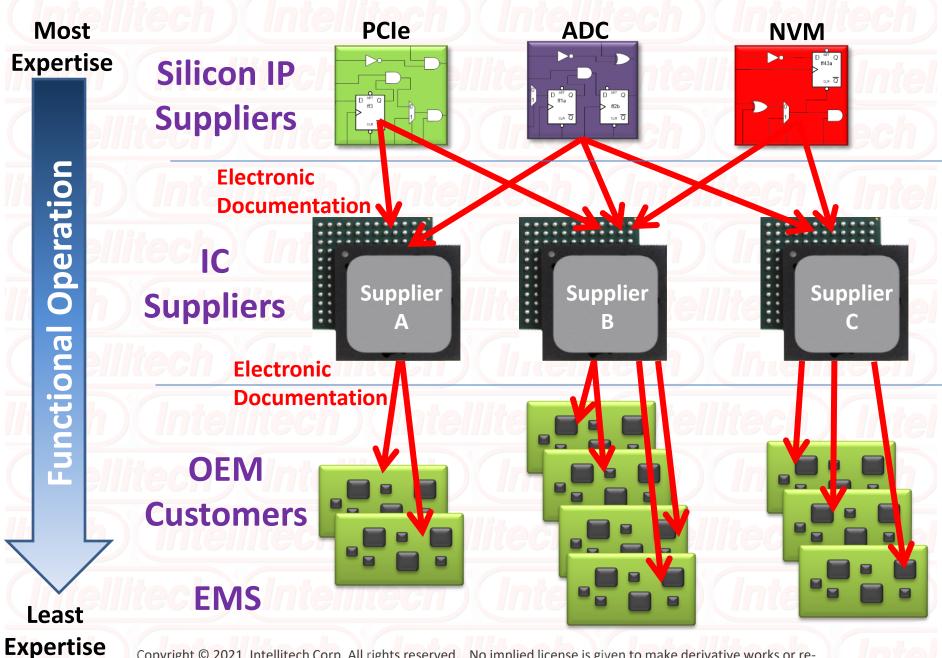

#### Why standardize documentation?

- No time to read 1000 page PDFs

- No time to learn/build tools around different formats of a dozen IC suppliers

- SoC customers need scale-able automation

- Can't be an expert in all technologies

- PDF specifications have errors/ambiguities

- Need single format to Use @ silicon debug, wafer test, customer PCB bring-up, customer PCB test, etc.

#### ntellitech) (Intellitech

Vendor B

PDF files +

Examples +

Program NVRAM

#### Vendor C

RISC-V C++ Tools + PDF With GUI App, program

\*\*PDF\*\*

\*\*Vendor D\*\*

\*\*Vendor D\*\*

\*\*Vendor D\*\*

\*\*Vendor D\*\*

\*\*POF\*\*

\*\*Postarian discourse of the second of the se

# Vendor A

ARM C++

Toolchain,

+ PDF +

Custom flash

programming

PDF Files

+ Proprietary

STIL patterns

PDF Files + VCD + XML

# **PDF Documentation IC Supplier** Error/ **PDF Ambiguity OEM** Customer

# Standards Documentation IC Supplier Error/ Ambiguity

**Validate**

w/ IC or Sim

BSDL

& PDL

# What customers are saying:

"Debug of third party IP on ATE has consistently been a bottleneck to productivity. We see the IEEE 1149.1-2013 standard as a critical specification for efficient use of third party IP. The Intellitech toolset provides us with a methodology to link to simulation for pre-silicon validation of the IP and our ASICs. Having a common source for the verification environment and the test environment accelerates test debug an order of magnitude faster compared to traditional methods."

Mike Fung

ASIC Test and Characterization Manager

Teradyne

# What/Why IEEE 1149.10-2017?

IEEE Standard for High-Speed Test Access Port and On-Chip Distribution Architecture — 80+ industry experts approved

- Incorporate IEEE 1149.1-2013 by reference

- Remove requirement for TAP

- Remove requirement boundary register

- Add support for SERDES packets

- Add synchronous serial interfaces (SPI, I2C, SPMI, etc)

#### What's the motivation?

- Not all ICs have JTAG pins

- Many ICs and SoCs have non-digital pins

- Reduce IC design requirement.

- a. Mission mode interface has access!

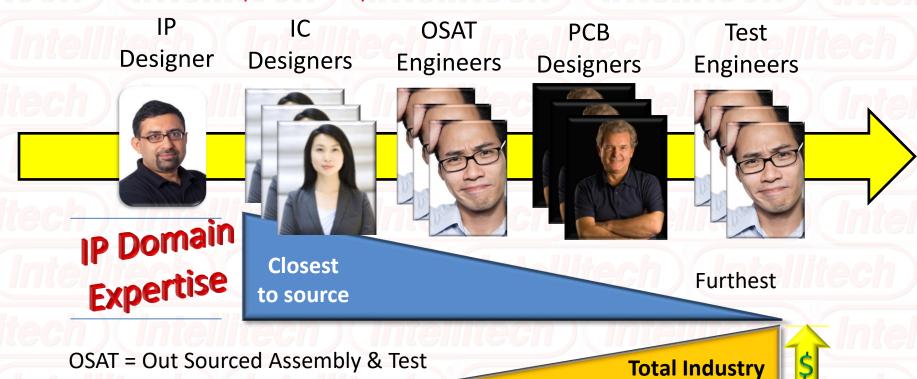

#### Standards enable more reliable information transfer

#### IP and IC designers can transfer critical expertise to customers

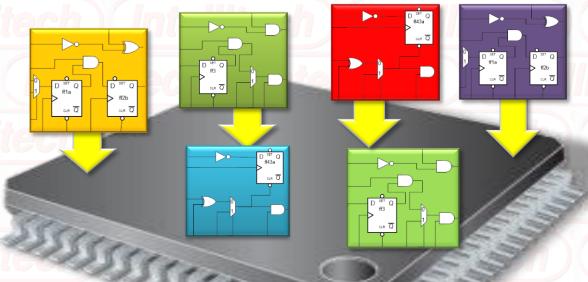

One 1149.x compliant IP gets leveraged across hundreds of engineers One 1149.x compliant IC may have hundreds or thousands of IP

WORM = Write Once Read Many!

Copyright © 2021 Intellifect Corp. All rights reserved. No implied license is given to make derivative works or redistribute these slides in whole or in part. These slides may be used as an occasional memory refresher for personal use only.

**Cost Savings**

# **Compile and Go!**